PJON

PJON Protocol Embraces Hardware with New Verilog Implementation

The PJON protocol, known for its single-wire data link, now boasts a hardware implementation in Verilog, enhancing inter-processor communication.

- Read time

- 7 min read

- Word count

- 1,464 words

- Date

- Dec 13, 2025

Summarize with AI

The Padded Jittering Operative Network (PJON) protocol, celebrated for its efficient single-wire communication, has taken a significant leap forward with a new hardware implementation in Verilog. This development, specifically for the PJDL (Padded Jittering Data Link) bus, offloads low-level tasks from software, providing a dedicated peripheral for inter-processor communication. The module has been successfully integrated into the CROC chip project, an educational System-on-Chip initiative, making this versatile protocol even more accessible and robust for hardware-level applications. This advancement streamlines data handling for up to 255 devices, marking a crucial evolution for the decade-old PJON.

🌟 Non-members read here

PJON Protocol Achieves Hardware Integration with Verilog Module

The Padded Jittering Operative Network, or PJON, a protocol long admired for its single-data-line simplicity akin to the OneWire standard, has announced a significant advancement. This protocol, capable of managing up to 255 devices on a single wire, now benefits from a hardware implementation. This development, specifically targeting the PJDL (Padded Jittering Data Link) bus, moves much of the protocol’s complexity from software to hardware.

Traditionally, single-wire protocols like PJON require frequent bus checks, which translates to a trade-off where software complexity compensates for hardware simplicity. With the introduction of this Verilog implementation, this concern is substantially mitigated. Engineers and developers can now leverage a dedicated PJDL peripheral for their inter-processor communication needs, streamlining the design process and enhancing efficiency. This integration marks a crucial step in making the PJON protocol even more versatile and accessible for a broader range of hardware projects. The project’s creator, Giovanni, highlighted this new phase, which promises to simplify development for those working with embedded systems.

The Verilog module effectively offloads many low-level PJDL tasks, creating a dedicated hardware component. This peripheral simplifies the integration of PJON into various systems, offering a more robust and efficient communication solution. This advancement is particularly noteworthy for developers seeking to optimize performance and reduce the processing load on microcontrollers. By abstracting the complex timing and data handling into a hardware block, the new implementation allows for more reliable and higher-speed data exchanges.

Furthermore, this hardware module has already been successfully taped out. It forms part of the CROC chip project, an educational System-on-Chip initiative. This real-world application demonstrates the module’s viability and robustness, providing a tangible example of its practical utility. The successful tape-out is a testament to the design’s maturity and its readiness for broader adoption in the embedded systems community. This development is set to benefit both educational endeavors and commercial applications alike, offering a tested and proven solution.

Advancing Single-Wire Communication

PJON has established itself as a remarkably flexible and efficient communication protocol over the past decade. Its ability to operate on a single wire makes it ideal for applications where minimizing wiring and complexity is crucial. This simplicity, however, often came with the caveat of increased software overhead to manage the bus and ensure data integrity. The new Verilog implementation directly addresses this challenge, transforming the protocol’s operational paradigm.

The core advantage of single-wire protocols lies in their minimal hardware requirements, reducing material costs and simplifying circuit board designs. PJON pushes this further by supporting a substantial number of devices on a single shared data line, making it suitable for distributed sensor networks and control systems. The protocol’s design inherently manages potential data collisions through its “Padded Jittering” mechanism, ensuring reliable data transfer even in busy environments. This mechanism introduces small, random delays that help prevent simultaneous transmissions, maintaining data integrity without complex arbitration hardware.

Historically, the software libraries handling PJON’s low-level operations were responsible for precise timing and data serialization. While effective, this approach consumed significant microcontroller resources and introduced potential latencies depending on the processor’s workload. The new hardware peripheral takes over these time-critical tasks, executing them with dedicated logic. This frees up the main processor to handle higher-level application logic, leading to more responsive and powerful embedded systems. The shift from software-driven timing to hardware-driven precision significantly enhances the protocol’s performance and reliability, particularly in real-time applications.

The successful integration into an educational SoC project like CROC underscores the module’s accessibility and its potential to foster learning. Students and researchers can now explore the intricacies of bus protocols with a ready-made, high-performance hardware block, accelerating their understanding and development cycles. This makes the PJON Verilog module a valuable tool for both academic and industrial contexts, bridging the gap between theoretical knowledge and practical application. The open-source nature of such projects further encourages collaboration and innovation within the embedded systems community.

Technical Deep Dive into the PJDL Hardware Module

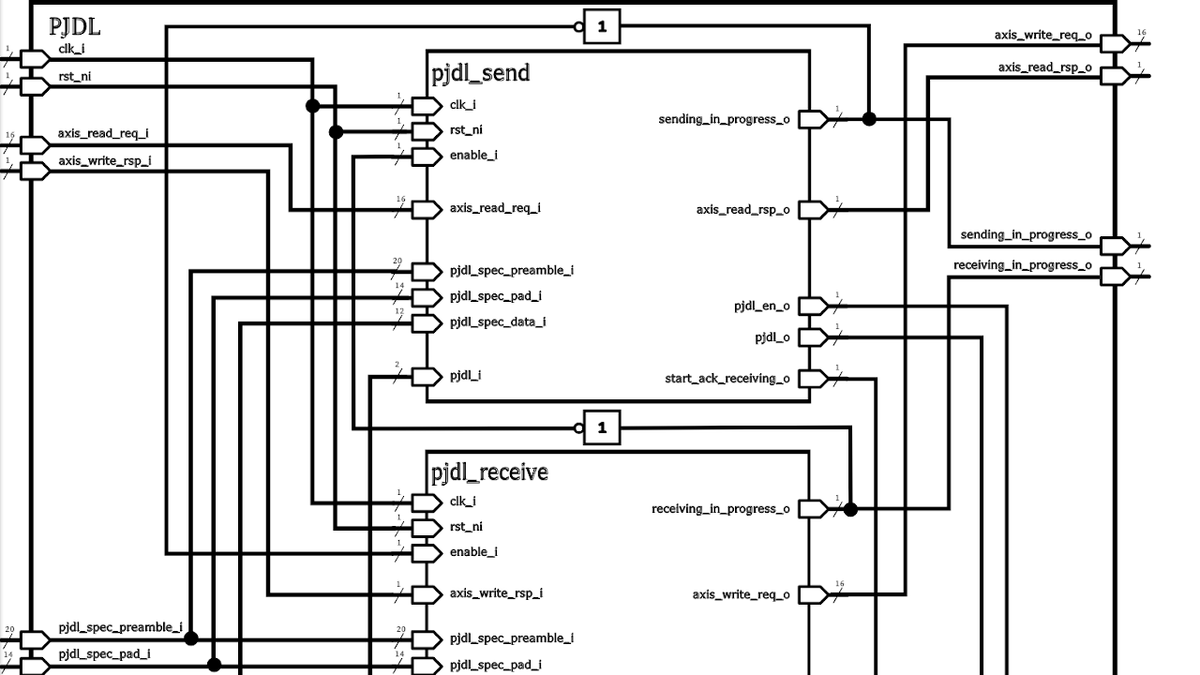

The Padded Jittering Data Link (PJDL) is a fundamental layer of the PJON protocol, specifically responsible for the actual data transmission and reception over the physical medium. Implementing PJDL in Verilog means that the intricate timing, data framing, and error checking mechanisms are now encapsulated within a dedicated hardware block. This hardware-centric approach brings several tangible benefits, including increased speed, improved timing accuracy, and reduced CPU utilization. These advantages are critical for high-performance and power-sensitive embedded applications.

Verilog, as a hardware description language, allows for a precise definition of digital circuits. By implementing PJDL in Verilog, developers create a physical circuit that handles the protocol’s requirements directly at the gate level. This means that operations like bit-banging, parity checking, and collision detection are no longer performed by software loops but by dedicated logic gates operating in parallel. The result is significantly faster data throughput and more consistent timing, regardless of other software tasks running on the microcontroller. This deterministic behavior is a key requirement for reliable communication in industrial and mission-critical systems.

One of the challenges in software-based single-wire protocols is managing jitter, which refers to variations in signal timing that can lead to data corruption. PJON’s “jittering” mechanism is designed to mitigate this by introducing controlled random delays. When this mechanism is moved to hardware, it can be implemented with higher precision and less variability than software approximations. The Verilog module can incorporate dedicated timers and state machines that accurately manage these delays and ensure proper synchronization between devices on the bus. This leads to a more robust communication link that is less susceptible to environmental noise and system load fluctuations.

The PJDL hardware module effectively acts as an accelerator for PJON communication. It presents a simplified interface to the main processor, allowing data to be written to and read from registers rather than requiring direct manipulation of GPIO pins and complex timing loops. This abstraction greatly simplifies the software development process, as engineers can interact with the PJDL peripheral at a higher level, focusing on the application logic instead of low-level bus management. The module handles all the gritty details, from start-bit detection to checksum verification, ensuring data integrity and reliable packet delivery.

The successful tape-out within the CROC chip project further validates the design’s integrity and performance. Taping out a chip means that the Verilog code has been synthesized into a physical layout, fabricated, and tested. This rigorous process confirms that the hardware implementation functions as intended and meets all specified design parameters. For the embedded systems community, this provides a highly reliable and proven solution for integrating PJON capabilities into custom silicon designs. This move from a software-centric protocol to a hardware-accelerated one represents a significant evolution, solidifying PJON’s position as a robust option for various communication needs.

Future Implications and Accessibility

The availability of a Verilog-based hardware implementation for PJON’s PJDL bus is poised to expand the protocol’s adoption across various domains. By offering a solution that minimizes software overhead and enhances performance, this development makes PJON more appealing for applications that demand high reliability, real-time response, and efficient resource utilization. This includes areas such as industrial automation, smart home devices, automotive systems, and advanced sensor networks, where every bit of performance and power savings counts.

For embedded system developers, this hardware module opens up new avenues for design optimization. Instead of dedicating valuable CPU cycles to manage a communication bus, they can now offload these tasks to a dedicated hardware block. This allows microcontrollers to focus on their primary computational responsibilities, leading to more powerful and responsive applications. It also simplifies the development cycle, as the complexity of bit-level communication is abstracted away, allowing engineers to work with higher-level interfaces. The module’s integration capability with existing SoC designs further enhances its practical utility.

The inclusion of this module in educational projects like CROC is particularly significant. It provides a tangible, high-performance example for students and researchers exploring hardware-software co-design and bus protocols. Learning about PJON through a fully functional Verilog implementation can offer deeper insights into the intricacies of digital communication and hardware acceleration. This hands-on experience is invaluable for preparing the next generation of embedded system engineers and fostering innovation in the field. The open nature of such developments often encourages further contributions and improvements from the community.

Moreover, the increasing accessibility of FPGA development boards and custom ASIC fabrication services makes it easier for individuals and small teams to experiment with and deploy such hardware implementations. The Verilog module for PJDL could become a standard component in custom silicon designs, offering a low-cost, high-performance single-wire communication solution. This democratization of hardware development means that even smaller projects can benefit from the reliability and efficiency previously reserved for large-scale industrial applications. The decade-old PJON protocol continues to evolve, proving its enduring relevance and adaptability in the ever-changing landscape of embedded systems.